PHASE-LOCKED LOOP

1. Tujuan [KEMBALI]

- Untuk mengetahui fungsi PLL

- Untuk mengetahui prinsip kerja PLL

- Untuk mengetahui bentuk gelonbang input dan output

- IC NE565, adalah Komponen Elektronika Aktif yang terdiri dari gabungan ratusan,

ribuan bahkan jutaan Transistor, Dioda, Resistor dan Kapasitor yang

diintegrasikan menjadi suatu Rangkaian Elektronika dalam sebuah kemasan

kecil. Bahan utama yang membentuk sebuah Integrated Circuit (IC) adalah

Bahan Semikonduktor. Silicon merupakan bahan semikonduktor yang paling

sering digunakan dalam Teknologi Fabrikasi Integrated Circuit (IC).

Dalam bahasa Indonesia, Integrated Circuit atau IC ini sering

diterjemahkan menjadi Sirkuit Terpadu.

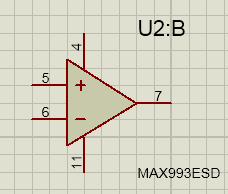

- Operational Amplifiler, MAX993E SD, adalah salah satu dari bentuk IC Linear yang berfungsi sebagai Penguat

Sinyal listrik. Sebuah Op-Amp terdiri dari beberapa Transistor, Dioda,

Resistor dan Kapasitor yang terinterkoneksi dan terintegrasi sehingga

memungkinkannya untuk menghasilkan Gain (penguatan) yang tinggi pada

rentang frekuensi yang luas. Dalam bahasa Indonesia, Op-Amp atau

Operational Amplifier sering disebut juga dengan Penguat Operasional.

- Kapasitor, Sebagai Penyimpan arus atau tegangan listrik. Sebagai Konduktor yang dapat melewatkan arus AC (Alternating Current) Sebagai Isolator yang menghambat arus DC (Direct Current)

- Resistor, membatasi atau mengatur arus dalam suatu rangkaian

- Sumber AC, adalah tegangan dengan aliran arus bolak-balik. Tegangan AC tidak

memiliki notasi/tanda seperti tegangan DC. Oleh karena itu pemasangan

tegangan AC pada rangkaian boleh terbalik kecuali untuk aplikasi

tegangan AC 3 phase pada motor listrik.

- Sumber DC, adalah tegangan dengan aliran arus searah. Tegangan DC memiliki notasi/tanda positif pada satu ttiknya dan negatif pada titik yang lain.

3. Dasar Teori [KEMBALI]

Phase-Locked Loop (PLL) adalah sirkuit elektronik yang terdiri dari detektor fase, filter low-pass, dan osilator yang dikendalikan tegangan terhubung seperti yang ditunjukkan pada Gambar 17.25.

Aplikasi umum PLL meliputi:

(1) synthesizer frekuensi yang memberikan tip mul dari frekuensi sinyal referensi [misalnya, frekuensi pembawa untuk beberapa saluran unit band warga (CB) atau unit band laut-radio-band dapat dihasilkan menggunakan frekuensi kristal tunggal yang dikendalikan dan kelipatannya dihasilkan menggunakan PLL];

(2) Jaringan demodulasi FM untuk operasi FM dengan linieritas yang sangat baik antara frekuensi sinyal in put dan tegangan keluaran PLL;

(3) demodulasi kedua data frekuensi transmisi atau pembawa dalam transmisi data digital yang digunakan dalam pergeseran frekuensi operasi penguncian (FSK); dan

(4) berbagai bidang termasuk modem, penerima dan pemancar uji coba teleme, pengurai nada, detektor AM, dan filter lacak.

Aplikasi umum PLL meliputi:

(1) synthesizer frekuensi yang memberikan tip mul dari frekuensi sinyal referensi [misalnya, frekuensi pembawa untuk beberapa saluran unit band warga (CB) atau unit band laut-radio-band dapat dihasilkan menggunakan frekuensi kristal tunggal yang dikendalikan dan kelipatannya dihasilkan menggunakan PLL];

(2) Jaringan demodulasi FM untuk operasi FM dengan linieritas yang sangat baik antara frekuensi sinyal in put dan tegangan keluaran PLL;

(3) demodulasi kedua data frekuensi transmisi atau pembawa dalam transmisi data digital yang digunakan dalam pergeseran frekuensi operasi penguncian (FSK); dan

(4) berbagai bidang termasuk modem, penerima dan pemancar uji coba teleme, pengurai nada, detektor AM, dan filter lacak.

Sinyal input, Vi, dan yang dari VCO, Vo, dibandingkan dengan pembanding fase (lihat Gbr. 17.25) memberikan tegangan output, Ve, yang mewakili fase perbedaan fase antara kedua sinyal. Tegangan ini kemudian diumpankan ke filter low-pass yang memberikan tegangan output (diperkuat jika perlu) yang dapat diambil sebagai usia volt keluaran dari PLL dan digunakan secara internal sebagai tegangan untuk memodulasi frekuensi bebas VCO . Operasi loop tertutup dari sirkuit adalah untuk mempertahankan frekuensi VCO dikunci dengan frekuensi sinyal input.

Operasi PLL dasar

Operasi

dasar sirkuit PLL dapat dijelaskan dengan menggunakan sirkuit Gambar

17.25 sebagai referensi. Kami pertama-tama akan mempertimbangkan operasi

berbagai sirkuit dalam loop fase terkunci ketika loop beroperasi dalam

kunci (frekuensi sinyal input dan Frekuensi VCO sama). Ketika frekuensi

sinyal input sama dengan itu dari VCO ke komparator, tegangan, Vd,

diambil sebagai output adalah nilai yang dibutuhkan untuk menahan VCO

terkunci dengan sinyal input. VCO kemudian memberikan output dari sebuah

sinyal gelombang persegi amplitudo tetap pada frekuensi input. Operasi

terbaik adalah diperoleh jika frekuensi fopusat

VCO, untuk diatur dengan tegangan bias dc di tengah rentang operasi

liniernya. Penguat memungkinkan penyesuaian tegangan dc dari itu

diperoleh sebagai output dari rangkaian filter. Ketika loop terkunci,

dua sinyal ke komparator memiliki frekuensi yang sama, meskipun tidak

harus dalam fase. A diperbaiki Perbedaan fasa antara dua sinyal ke hasil

komparator dalam usia dc volt tetap ke VCO. Perubahan frekuensi sinyal

input kemudian menghasilkan perubahan dalam tegangan dc ke VCO. Dalam

rentang frekuensi tangkap dan kunci, tegangan dc akan mengarahkan

frekuensi VCO agar sesuai dengan input.

Sementara loop berusaha mencapai kunci, output dari pembanding fase berisi komponen frekuensi pada jumlah dan perbedaan sinyal yang dibandingkan. Filter low pass hanya melewati komponen frekuensi rendah dari sinyal sehingga loop dapat memperoleh kunci antara sinyal input dan VCO.

Karena rentang operasi terbatas VCO dan koneksi umpan balik darisirkuit PLL, ada dua pita frekuensi penting yang ditentukan untuk PLL. Itukisaran tangkapan PLL adalah rentang frekuensi yang berpusat tentang VCO yang berjalan bebas frekuensi fo, untuk di mana loop dapat memperoleh kunci dengan sinyal input. Setelah itu PLL telah mencapai tangkapan, itu dapat mempertahankan kunci dengan sinyal input lebih dari yang agak rentang frekuensi yang lebih luas disebut rentang kunci.

Aplikasi

DEMODULASI FREKUENSI

Demodulasi

atau deteksi FM dapat langsung dicapai menggunakan sirkuit PLL. Jika

frekuensi pusat PLL dipilih atau dirancang pada frekuensi pembawa FM,

fil tered atau tegangan keluaran dari Gambar 17.25 adalah umur volt yang

didemodulasi yang diinginkan, dengan variasi nilainya sebanding dengan

variasi frekuensi sinyal. PLL sirkuit dengan demikian beroperasi sebagai

strip, frekuensi limiter, dan modulator frekuensi menengah lengkap (IF)

seperti yang digunakan pada penerima FM.

Satu

unit PLL yang populer adalah 565, ditunjukkan pada Gambar. 17.26a. 565

berisi fase detektor, amplifier, dan osilator yang dikendalikan

tegangan, yang hanya sebagian terkoneksi secara internal. Sebuah

resistor dan kapasitor eksternal, R1 dan C1, digunakan untuk mengatur berjalan bebas atau frekuensi tengah VCO. Kapasitor eksternal lain, C2,

digunakan untuk mengatur passband filter low-pass, dan output VCO harus

dihubungkan kembali sebagai masukan ke detektor fase untuk menutup loop

PLL. 565 biasanya menggunakan dua daya persediaan, V+ dan V-.

SINTESIS FREKUENSI

Sebuah

synthesizer frekuensi dapat dibangun di sekitar PLL seperti yang

ditunjukkan pada Gambar. 17.27. Pembagi frekuensi bebas dimasukkan

antara output VCO dan pembanding fase sehingga sinyal loop ke pembanding

adalah pada frekuensi fo sementara output VCO adalah Nfo. Ini output adalah kelipatan dari frekuensi input selama loop terkunci. Input sinyal dapat distabilkan pada f1 dengan output VCO yang dihasilkan pada Nf1 jika loop diatur untuk mengunci pada frekuensi fundamental (ketika fo = f1). Gambar 17.27b menunjukkan contoh menggunakan 565 PLL sebagai pengali frekuensi dan 7490 sebagai pembagi. Input Vi pada frekuensi f1 dibandingkan dengan input (frekuensi fo) pada pin 5. Output pada Nfo (4fo dalam

contoh ini) dihubungkan melalui rangkaian inverter untuk memberikan

input pada pin 14 dari 7490, yang bervariasi antara 0 dan +5 V.

Menggunakan output pada pin 9, yang dibagi dengan 4 dari yang di input

ke 7490, sinyal di pin 4 dari PLL adalah empat kali frekuensi input

selama loop tetap terkunci. Sejak VCO dapat bervariasi hanya pada

rentang terbatas dari frekuensi pusatnya, mungkin perlu untuk mengubah

frekuensi VCO setiap kali nilai pembagi diubah. Selama sirkuit PLL

terkunci, frekuensi output VCO akan persis N kali frekuensi in put. Anda

hanya perlu menyesuaikan kembali agar fo berada dalam daerah tangkap dan kunci, loop tertutup kemudian menghasilkan output VCO menjadi tepat Nf1 di kunci.

DEKORASI FSK

Dekoder

sinyal FSK (key-shift keyed) dapat dibuat seperti yang ditunjukkan pada

Gambar 17.28. Dekoder menerima sinyal di salah satu dari dua frekuensi

pembawa yang berbeda, 1270 Hz atau 1070 Hz, mewakili level atau tanda

logika RS-232C (-5 V) atau spasi (+14 V), masing-masing. Ketika sinyal

muncul di input, loop terkunci ke frekuensi input dan melacaknya di

antara dua frekuensi yang mungkin dengan pergeseran dc yang sesuai di

keluaran.

Filter tangga RC (tiga bagian C = 0,02 µF dan R = 10 kΩ) digunakan untuk menghapus komponen frekuensi penjumlahan. Frekuensi bebas berjalan disesuaikan dengan R1 sehingga

level tegangan dc pada output (pin 7) sama dengan pada pin 6. Lalu

input pada frekuensi 1070 Hz akan mendorong tegangan output decoder ke

level tegangan yang lebih positif, mendorong output digital ke level

tinggi (spasi atau +14 V). Sebuah masukan pada 1270 Hz akan mendorong

keluaran 565 dc kurang positif dengan output digital, yang kemudian

turun ke level rendah (tandai atau -5 V).

4. Prinsip Kerja [KEMBALI]

Bila dilihat dari fungsi masing-masing bagian diatas dapat digambarkan bahwa frekuensi yang berada dalam “lingkar” tersebut sangatlah stabil menyamai kestabilan frekuensi referensi dari osilator kristal. Yang paling menentukan dari kualitas sebuah PLL adalah Respone Time dari LPF dan Devider dan lebar bidang kerja dari VCO pada taraf tegangan yang mengendalikannya.

Perancangan dari nilai komponen pembangun LPF sangat menentukan terhadap keluaran PLL (VCO) secara langsung. Ketidak tepatan akan menyebabkan Locking Time berlangsung cukup lama dan ini merupakan indikasi unjuk kerja PLL yang kurang baik. Disamping juga bisa menyebabkan terjadinya side-tone yang cukup mengganggu karena akan ikut terbawa bersama gelombang pemodulasi pada Penerapan FM.

5. Rangkaian [KEMBALI]

- Buat rangkaian seperti gambar di bawah

- Jalankan rangkaiannya untuk melihat perubahan sinyal gelombang.

6. Video simulasi [KEMBALI]

7. Rangkaian [KEMBALI]

Konsep kerja : 565

berisi fase detektor, amplifier, dan osilator yang dikendalikan

tegangan, yang hanya sebagian terkoneksi secara internal. Sebuah

resistor dan kapasitor eksternal, R1 dan C1, digunakan untuk mengatur berjalan bebas atau frekuensi tengah VCO. Kapasitor eksternal lain, C2,

digunakan untuk mengatur passband filter low-pass, dan output VCO harus

dihubungkan kembali sebagai masukan ke detektor fase untuk menutup loop

PLL. 565 biasanya menggunakan dua daya persediaan, V+ dan V-.

8. Link Download [KEMBALI]

File HTML

File Rangkaian Simulasi Vidio Rangkaian Simulasi

Data sheet

Tidak ada komentar:

Posting Komentar